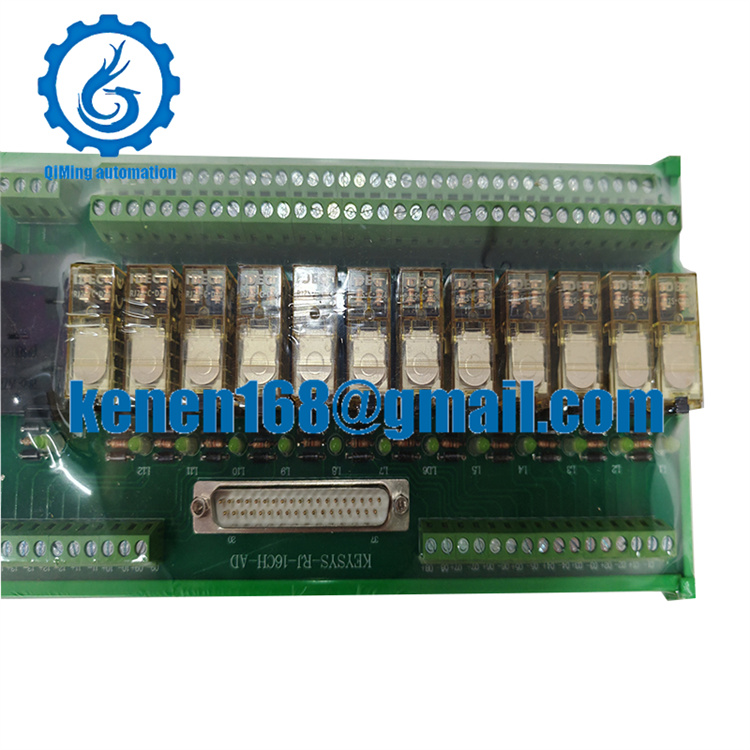

KEYSYS-RJ-16CH-AD KEYSYS terminal block

PCI Memory Mapping Architecture

The PCI memory mapping is governed by two core components:

- Hawk ASIC – Integrates the MPU/PCI bus bridge controller

- Universe ASIC – Serves as the PCI/VME bus bridge

These devices dynamically configure system memory mapping via programmable map decoder registers to accommodate application-specific requirements.

Key Characteristics:

- No default mapping: The PCI memory map is non-persistent; resetting the system disables all map decoders.

- Post-reset initialization: Software must reprogram the map decoders to establish application-specific memory mapping.

KEYSYS-RJ-16CH-AD KEYSYS terminal block

KEYSYS-RJ-16CH-AD KEYSYS terminal block

Here’s a professional technical rewrite in English:

Universe ASIC Configuration Protocol

1. Platform-Specific Memory Mapping

• Board architecture dependency:

- MVME2700 series: PReP-compliant memory mapping

- MVME5100 series: CHRP-standard memory mapping

• Functional definition: Determines PCI memory space visibility from processor perspective

2. PCI-VME Bridge Architecture

The Universe ASIC implements bidirectional address translation through:

| Bridge Direction | Control Registers | Functionality |

|---|---|---|

| PCI → VME | PCI Slave Registers | – Define address filtering thresholds for PCI-to-VME transfers – Configure VMEbus master addressing mode (A16/A24/A32) |

| VME → PCI | VME Slave Registers | – Establish VME-to-PCI address translation protocols – Implement PCI master cycle conversion logic |

3. Address Translation Mechanics

• PCI domain:

- Filters local PCI bus transactions using programmed address windows

- Applies configured offset/base adjustments before VME forwarding

• VME domain: - Implements dynamic bus sizing (D8/D16/D32) during PCI transfers

- Supports block transfer modes (BLT/MBLT) through burst mapping

KEYSYS-RJ-16CH-AD KEYSYS terminal block

KEYSYS-RJ-16CH-AD KEYSYS terminal block

Address Translation Protocol for PCI/VME Bridging

1. Translate Register Configuration

The Translate register defines the offset required to map source addresses to the target bus domain.

2. Platform-Specific Translation Mechanics

| Operation Mode | Bus Direction | Key Constraint |

|---|---|---|

| PCI Slave Image | PCI → VME | Zero-offset mapping: |

VME_address = PCI_address & 0x00FFFFFF |

||

| (Upper 8-bit truncation via address mask) | ||

| VME Slave Image | VME → PCI | Base-relative translation: |

PCI_address = VME_address + Translate_Value |

3. Implementation by Platform

A. MVME2700 (PReP Architecture)

| Component | Address Space |

|---|---|

| PCI Local Bus | 0x80000000 (Local Memory Base) |

| VME Slave Translation | |

Translate_Value = 0x70000000 |

|

| Example: | |

VME: 0x10000000 → PCI: 0x10000000 + 0x70000000 = 0x80000000 |

|

| (Carry bit truncation at 32-bit boundary) |

B. MVME5100 (CHRP Architecture)

| Component | Address Space |

|---|---|

| PCI Local Bus | 0x00000000 (Local Memory Base) |

| VME Slave Translation | |

Translate_Value = 0xEC000000 |

|

| Example: | |

VME: 0x14000000 → PCI: 0x14000000 + 0xEC000000 = 0x00000000 |

|

| (64-bit result 0x100000000 truncated to 32-bit 0x00000000) |

4. Critical Implementation Notes

- Carry propagation suppression:

Hardware automatically discards overflow bits beyond configured bus width - Raven ASIC behavior:

Interprets translated PCI addresses as absolute local memory references

There are no reviews yet.